1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

|

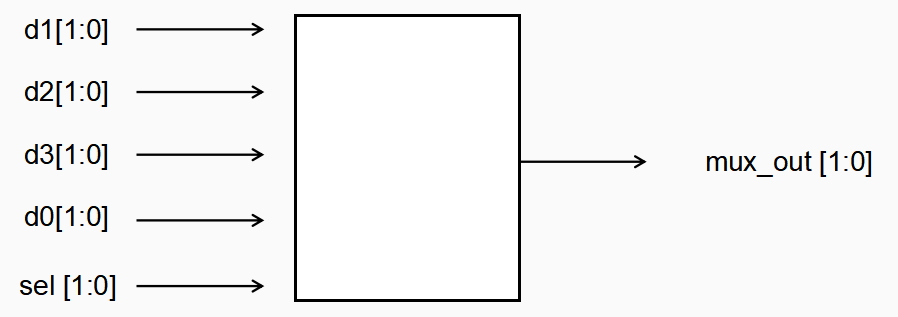

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output [1:0]mux_out

);

assign mux_out = (sel == 2'b00) ? d3 : ((sel == 2'b01) ? d2 : (sel == 2'b10) ? d1 : d0);

endmodule

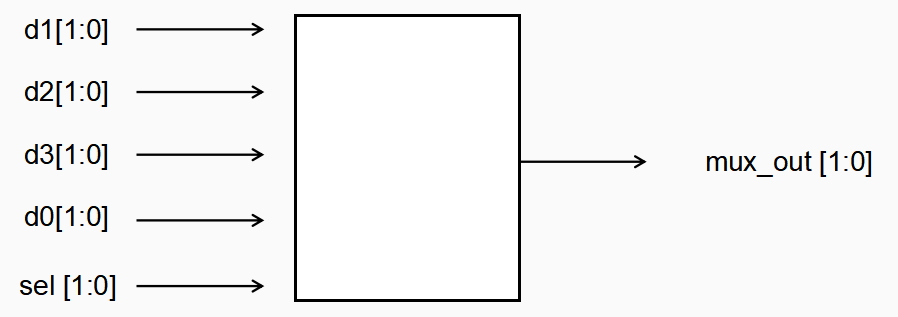

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output [1:0]mux_out

);

reg [1:0] mux_out_reg;

always @ (*)

begin

case(sel)

2'b00:mux_out_reg = d3;

2'b01:mux_out_reg = d2;

2'b10:mux_out_reg = d1;

2'b11:mux_out_reg = d0;

default : mux_out_reg = d0;

endcase

end

assign mux_out = mux_out_reg;

endmodule

|